# **Digital Integrated Circuits**

Monolithic Silicon CD4057AD CD4057AK CD4057AH

## COS/MOS LSI 4-Bit Arithmetic Logic Unit

Applications:

- Parallel Arithmetic Units

- Process Controllers

#### Features:

- LSI Complexity on a Single Chip

- 16-Instruction Capability

-Add, Subtract, Count

-AND, OR, Exclusive-OR

-Right, Left, or Cyclic Shifts

Remote Data Sets

- Graphic Display Terminals

- Bidirectional Data Busses

- Instruction Decoding on Chip

- Fully Static Operation

- Single-Phase Clocking

RCA-CD4057A is a low-power arithmetic logic unit (ALU) designed for use in LSI computers. An arithmetic system of virtually any size can be constructed by wiring together a number of CD4057A ALU's. The CD4057A provides 4-bit arithmetic operations, time sharing of data terminals, and full functional decoding for all control lines. The distributed control system of this device provides great flexibility in system designs by allowing hard-wired connection of N units in 4N unique combinations. Four control lines provide 16 instructions which include Addition, Subtraction, Bidirectional and Cycle Shifts, Up-Down Counting, AND, OR, and Exclusive-OR logic operations.

- Easily Expandable to 8, 12, 16, . . . Bit Operation

- Conditional-Operation Controls on Chip

- Low Quiescent Device Dissipation . . . 10 μW (typ) at

V<sub>DD</sub> = 10 V

- Add Time (Data In-To Sum Out) = 375 ns (typ) at 10V

- All Terminals Protected Against Static Discharge

- High Noise Immunity . . . 45% of V<sub>DD</sub> (typ) Over Full Temperature Range

- Operation from Single Positive or Negative Power Supply . . . 3 V to 15 V

- Full Military Temperature Range . . . -55°C to +125°C

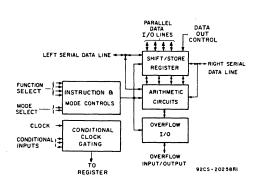

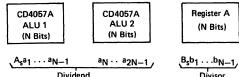

Fig. 1 — Block diagram — CD4057A.

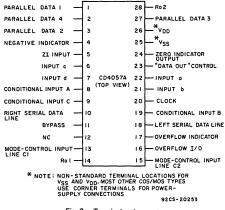

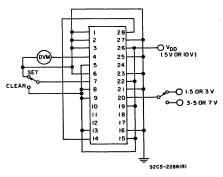

Fig. 2 - Terminal assignments.

Two mode control lines allow the CD4057A to function as any 4-bit section of a larger arithmetic unit by controlling the bidirectional serial transfer of data to adjacent arithmetic arrays. By means of three "Conditional Control" lines Overflow, All Zeros, and Negative State conditions may be detected and used to establish a conditional operation. Predetermined operation of the CD4057A on a conditional basis allows greater ALU flexibility. Although especially applicable as a parallel arithmetic unit, the CD4057A also finds use in virtually any application requiring one or more of its 16 basic instructions. The CD4057A is supplied in a hermetically sealed 28-lead dual-in-line ceramic package (CD4057AD), in a flat-pack (CD4057AK), and in chip form (CD4057AH).

#### MAXIMUM RATINGS, Absolute Maximum Values:

| STORAGE-TEMPERATURE RANGE                     |

|-----------------------------------------------|

| DISSIPATION PER PACKAGE                       |

| DC SUPPLY-VOLTAGE RANGE (VDD-VSS)0.5 to +15 V |

| ALL INPUTS $v_{ss} \leq v_1 \leq v_{DD}$      |

| Lead Temperature (During soldering)           |

| At distance 1/16 ± 1/32 inch (1.59 ± 0.79 mm) |

| from case for 10 seconds max                  |

MINIMUM RECOMMENDED

| DC SUPPLY VOLTAGE (VDD-VSS) |  | 3 V |

|-----------------------------|--|-----|

|-----------------------------|--|-----|

|                                                      |                  |           |            | LIMITS             |                |               |              |              |             | UNITS                |              |       |             |    |

|------------------------------------------------------|------------------|-----------|------------|--------------------|----------------|---------------|--------------|--------------|-------------|----------------------|--------------|-------|-------------|----|

| CHARACTERISTIC                                       | SYMBOL           |           |            | CD4057AD, CD4057AK |                |               |              |              |             |                      |              |       |             |    |

|                                                      |                  |           | vo         | V <sub>DD</sub>    |                | - <u>55°(</u> |              | NAT:         | 25°C        |                      |              | 125°C |             |    |

|                                                      | _                |           | Volts      | Volts              | Min.           | Тур.          | Max.         | Min.         | Typ.<br>0.5 |                      | Min.         | Тур.  | Max.<br>150 |    |

| Quiescent Device<br>Current                          | ۱L               |           |            | 5<br>10            | -              |               | 3.7<br>7.5   | -            | 0.5<br>1    | 5<br>10 <sup>:</sup> | 1            | -     | 300         | μΑ |

| Quiescent Device<br>Dissipation/Package              | PD               |           |            | 5<br>10            |                |               | 18.5<br>75.0 |              | 2.5<br>10   | 2.5<br>100           |              | -     | 750<br>3000 | μW |

| Output Voltage:<br>Low-Level                         | V <sub>OL</sub>  |           |            | 5<br>10            |                | -             | 0.01         |              | -           | 0.01                 | -            |       | 0.05        | v  |

| High Level                                           | V <sub>OH</sub>  |           |            | 5                  | 4.99           |               | -            | 4.99<br>9.99 | 5<br>10     | -                    | 4.95<br>9.95 |       |             | v  |

| Noise Immunity                                       | VNIL             |           | 0.8        | 5                  | 1.5            | _             |              | 1.5          | 2.25        |                      | 1.4          | _     | _           |    |

| (All Inputs)<br>For Definition                       |                  |           | 1<br>4.2   | 10<br>5            | 3<br>1.4       | -             |              | 3<br>1.5     | 4.5<br>2.25 | -                    | 2.9<br>1.5   | -     | -           | v  |

| See Appendix                                         | V <sub>NIH</sub> | L         | 9          | 10                 | 2.9            |               | -            | 3            | 4.5         |                      | 3            | -     | -           |    |

| Output Drive Current:<br>Zero Indicator<br>n-channel | IDN              |           | 0.5        | 5                  | 0.11           | -             | -            | 0.09         | 0.16        | -                    | 0.06         | -     |             |    |

| p-channel                                            | IDP              |           | 3          | 5<br>10            | 0.04<br>0.08 ' |               |              | 0.03         | 0.06        | -                    | 0.02         | -     | -           |    |

| Negative Indicator                                   | IDN              | $\square$ | 0.5        | 5                  | 0.11           | -             | _            | 0.09         | 0.30        | _                    | 0.06         | -     |             |    |

| n-channel<br>p-channel                               | I <sub>D</sub> P | -         | 0.5        | 10<br>5            | 0.12           |               | -            | 0.10         | 0.40        |                      | 0.07         |       | -           |    |

|                                                      |                  |           | 9.5        | 10                 | 0.12           | -             | -            | 0.10         | 0.30        | -                    | 0.07         | -     | -           | mA |

| Overflow Indicator                                   | I <sub>D</sub> N |           | 0.5        | 5<br>10            | 0.25           | -             | -            | 0.20         | 0.50        |                      | 0.14         |       |             |    |

| p-channel                                            | IDP              | $\vdash$  | 4.5        | 5                  | 0.08           | -             | _            | 0.07         | 0.21        | -                    | 0.05         | _     | -           |    |

|                                                      |                  |           | 9.5        | 10                 | 0.12           | -             | -            | 0.10         | 0.38        | -                    | 0.07         | -     | -           |    |

| All Other Outputs                                    | IDN              |           | 0.5        | 5                  | 0.11           | -             | -            | 0.09         | 0.10        | -                    | 0.06         |       | <u> </u>    |    |

| n-channel                                            |                  |           | 0.5        | 10                 | 0.06           | -             | -            | 0.05         | 0.12        | -                    | 0.03         |       |             |    |

| p-channel                                            | I <sub>D</sub> P |           | 4.5<br>9.5 | 5<br>10            | 0.02           | -             | -            | 0.02         | 0.05        | -                    | 0.01         | -     |             |    |

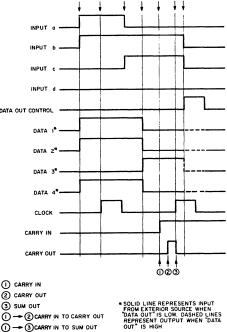

### DYNAMIC ELECTRICAL CHARACTERISTICS, at $T_A = 25^{\circ}C$ and $C_L = 15 \, pF$

Typical Temperature Coefficient at all values of  $V_{DD} = 0.3\%/^{\circ}C$

| CHARACTERISTICS                                                      | SYMBOLS                                           | TES<br>CONDIT | -                  | CD405<br>Min. | LIMITS<br>7AD, CD4<br>Tvp. | 057AK<br>Max.                | UNITS | CHARAC-<br>TERISTIC<br>CURVES<br>& TEST<br>CIRCUITS |

|----------------------------------------------------------------------|---------------------------------------------------|---------------|--------------------|---------------|----------------------------|------------------------------|-------|-----------------------------------------------------|

| Propagation Delay Time:<br>DATA IN-to-<br>SUM OUT                    | <sup>t</sup> PLH,                                 |               | 5                  |               | 1430<br>375                | <u>3900</u><br>720           |       | 10 a                                                |

| CARRY IN-to-<br>SUM OUT                                              | <sup>t</sup> PHL                                  |               | 5<br>10            |               | 915<br>310                 | 2550<br>840                  |       | 10 b                                                |

| DATA IN-to-<br>CARRY OUT                                             |                                                   |               | 5<br>10            |               | 950<br>265                 | 2580<br>720                  | ns    | 10 a                                                |

| CARRY IN-to-<br>CARRY OUT                                            |                                                   |               | 5<br>10            | -             | 485<br>175                 | 1320<br>480                  |       | 10 b                                                |

| ZI Input<br>-to-<br>ZI Output                                        | <sup>t</sup> PLH<br><sup>t</sup> PHL              |               | 5<br>10<br>5<br>10 | -             | 1980<br>750<br>265<br>110  | 5400<br>2040<br>720<br>300   |       |                                                     |

| Transition Time:<br>ZI Output                                        | <sup>t</sup> TLH<br><sup>t</sup> THL              |               | 5<br>10<br>5<br>10 |               | 3700<br>1650<br>420<br>220 | 10350<br>4500<br>1140<br>600 | ns    | 12                                                  |

| Negative Indicator and<br>Overflow Indicator<br>All Other<br>Outputs | <sup>t</sup> TLH <sup>,</sup><br><sup>t</sup> THL |               | 5<br>10<br>5<br>10 | -             | 300<br>165<br>1000<br>475  | 825<br>450<br>2775<br>1275   |       |                                                     |

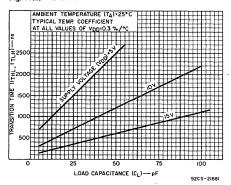

| Minimum Clock Pulse<br>Width                                         | <sup>t</sup> WL, <sup>t</sup> WH                  |               | 5                  | -             | 400                        | 1200<br>375                  | ns    | 13                                                  |

| Clock Rise and Fall Time                                             | t <sub>r</sub> CL, t <sub>f</sub> CL              |               | 5<br>10            |               |                            | 15<br>15                     | μs    | 13                                                  |

| Set Up Time :<br>DATA                                                | <sup>t</sup> SLH <sup>, t</sup> SHL               |               | 5<br>10            |               | 20<br>10                   | 40<br>20                     | ns .  | 14                                                  |

| OP CODE                                                              |                                                   |               | 5<br>10            |               | 1675<br>485                | 4590<br>1320                 | ns    | 14                                                  |

| Data Hold Time                                                       | <sup>t</sup> Dh                                   |               | 5<br>10            | -             | 20<br>10                   | 40<br>20                     | ns    | 15                                                  |

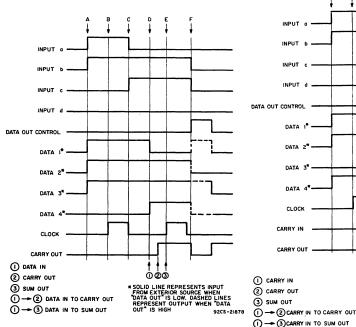

| Maximum Clock Frequency:<br>Count Mode                               | fCL                                               |               | 5<br>10            | 0.13<br>0.46  | 0.36                       |                              | MHz   | 11                                                  |

| Shift Mode                                                           | <sup>f</sup> CL                                   |               | 5<br>10            | 0.33<br>1.4   | 0.90<br>3.8                |                              | 10112 |                                                     |

| Input Capacitance                                                    | CI                                                | ANY I         | NPUT               | -             | 5                          | -                            | pF    |                                                     |

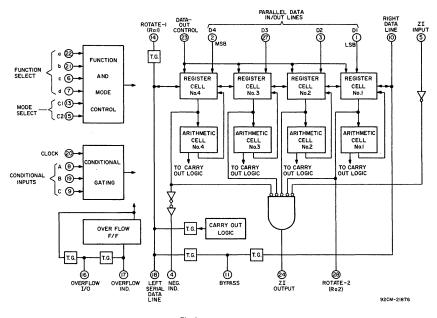

Fig. 3 - Simplified logic diagram.

#### LOGIC DESCRIPTION

#### **OPERATIONAL MODES**

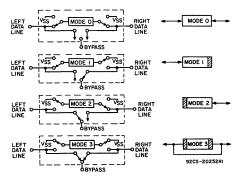

The CD4057A arithmetic logic unit operates in one of four possible modes. These modes control the transfer of information, either serial data or arithmetic operation carries, to and from the serial-data lines. Fig. 5 shows the manner in which the four modes control the data on the serial-data lines.

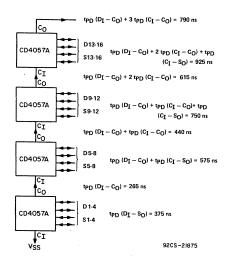

Fig. 4 – Typical speed characteristics of a 16-bit ALU at  $V_{DD} = 10$  V.

Fig. 5 - Schematic of "Mode" concept.

- In MODE 0, data can enter or leave from either the left or the right serial-data line.

- In MODE 1, data can enter or leave only on the left serialdata line;

- In MODE 2, data can enter or leave only on the right serialdata line.

- In MODE 3, serial data can neither enter nor leave the register, regardless of the nature of the operation. Furthermore, the register is by-passed electrically, i.e., there is an electrical bidirectional path between the right and left serial data terminals.

The two input lines labeled C1 and C2 in the terminal assignment diagram define one of four possible modes shown in Table I.

Through the use of mode control, individual arithmetic arrays can be cascaded to form one large processor or many processors of various lengths.

TABLE I - MODE DEFINITION

| C2 | C1 | MODE |

|----|----|------|

| 0  | 0  | 0    |

| 0  | 1  | 1    |

| 1  | 0  | 2    |

| 1  | 1  | 3    |

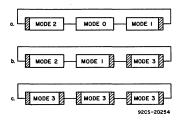

Examples of how one "hard-wired" combination of three ALU's can form (a) a 12-bit parallel processor, (b) one 8-bit and one 4-bit parallel processor, or (c) three 4-bit parallel processors, merely by changes in the modes of each ALU are shown in Fig. 6.

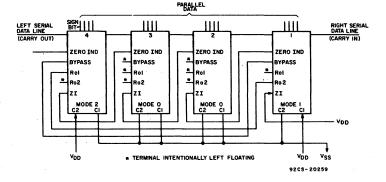

Fig.6- "Mode" connections for parallel processor: (a) 12-bit unit, (b) one 8-bit and one 4-bit unit (c) three 4-bit units. Data-flow interruptions are shown by shaded areas. With these three ALU's and the four available modes, 61 more system combinations can be formed. If 4 ALU's are used,  $4^4$  combinations (256) are possible. Fig. 7 shows a diagram of 4 CD4057A's interconnected to form a 16-bit parallel processor.

NOTE: The BYPASS terminal of the "most significant" CD4057A is connected to the bypass terminal of the "least significant" CD4057A. The bypass terminals on all other CD4057A's are left floating. This interconnection is performed whenever more than one CD4057A are used to form a processor.

#### INSTRUCTION REPERTOIRE

Four encoded lines are used to represent 16 instructions. Encoded instructions are as follows:

#### abcd

- 0 0 0 0 NO-OP (Operational Inhibit)

- 0001 AND

- 0 0 1 0 Count down

- 0 0 1 1 Count up

- 0 1 0 0 Subtract Stored number from zero (SMZ)

- 0 1 0 1 Subtract from parallel data lines (SM) (stored number from parallel data lines)

- 0 1 1 0 Add (AD)

- 0 1 1 1 Subtract (SUB) (Parallel data lines from stored number)

- 1 0 0 0 Set to all ones (SET)

- 1 0 0 1 Clear to all zeroes (CLEAR)

- 1 0 1 0 Exclusive-OR

- 1011 OR

- 1 1 0 0 Input Data (From parallel data lines)

- 1 1 0 1 Left shift

- 1 1 1 0 Right shift

- 1 1 1 1 Rotate (cycle) right

All instructions ar executed on the positive edge of the clock.

#### PARALLEL COMMANDS

- a. CLEAR sets register to zero.

- b. SET sets register to all ones.

- c. OR processes contents of register with value on parallel-data lines in a logical OR function.

- AND processes contents of register with value on parallel-data lines in a logical AND function.

- e. Exclusive-OR processes contents of register with data on parallel-data lines in a logical Exclusive-OR function.

- f. IN loads data on parallel-data lines into register.

- g. DATA OUT CONTROL unloads contents of register and overflow flip-flop onto parallel data lines and overflow I/O independent of all other controls.

- h. SUB:

- In Mode 0, adds to the contents of the register the one's complement of the data on the parallel-data lines. Carries can enter on the right serial data line and can leave on the left serial data line. The overflow indicator does not change state.

- In Mode 1, adds to the contents of the register the two's complement of the data on the parallel-data lines. Generated carries can leave on the left serial line. The CARRY IN is set to zero. The overflow indicator does not change state.

- In Mode 2, same as Mode 0, except carries cannot leave on the right serial-data line. The absence or presence of an overflow is registered.

- In Mode 3, same as Mode 1, except carries cannot leave on the left serial-date line. The absence or presence of an overflow is registered.

#### i. COUNT UP:

- In Mode 0, adds to the contents of the register the data on the right serial-data line and permits any resulting carry to leave on the left serial-data line. No data enters the parallel-data lines.

- In Mode 1, internally adds a one to the contents of the register and permits any resulting carry to leave on the left serial-data line. No data enters or leaves the right serial-data line.

- In Mode 2, adds to the contents of the register the data on the right serial-data line. No data enters or leaves the left serial-data line.

- In Mode 3, internally adds a one to the contents of the register. No data enters or leaves the register on any serial-data or parallel-data line.

In all modes, with the DATA OUT control "high" the count is presented on the parallel data lines (D1-D4).

#### j. COUNT DOWN:

- In Mode 0, subtracts a one (2's complement form) from the contents of the register and adds to this result the data on the right serialdata line and permits any resulting carry to leave on the left serial-data line. No data enters on the parallel-data lines.

- In Mode 1, internally subtracts a one from the contents of the register and permits any resulting carry to leave on the left serial-data line. No data enters or leaves the right serial-data line.

- In Mode 2, subtracts a one from the contents of the register and adds to this result the data on the right serial-data line. No data enters or leaves on the left serial-data line.

- In Mode 3, internally subtracts a one from the contents of the register. No data enters or leaves on the serial-data lines.

In all modes, with the DATA OUT control "high" the count is presented on the parallel data lines (D1-D4).

- k. ADD (AD):

- In Mode 0, adds the contents of the register to the data on the parallel-data lines and the right serial-data line. Any resulting carry can leave on the left serial-data line. The overflow indicator does not change state.

- In Mode 1, adds the contents of the register to the data on the parallel-data lines and allows any resulting carry to leave on the left serial-data line. The right serial-data line is opencircuited. The overflow indicator does not change state. The CARRY-IN is set to zero.

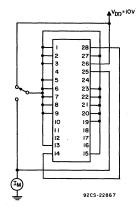

Fig.7 - Connection for 16-bit Arithmetic Logic Unit.

- In Mode 2, adds the contents of the register to the data on the parallel data lines and the right serial data line. Any overflow sets the overflow indicator. The left serial data line is opencircuited. The absence or presence of an overflow is registered.

- In Mode 3, adds contents of the register to the data on the parallel-data lines. Any resulting carry sets the overflow indicator. The two serialdata lines are open circuited. The absence or presence of an overflow is registered. The CARRY–IN is set to zero.

- SM— same operation as AD except the contents of the register are two's complemented during addition in Mode 1 and Mode 3. In Mode 0 or Mode 2, the contents of the register are one's complemented and added to the data on the right serial-data line and the parallel-data lines. Overflows occurring in Mode 1 or Mode 0 do not alter the overflow indicator. The presence or absence of overflows is registered on the overflow indicator in Mode 2 or Mode 3.

- m. SMZ:

- In Mode 0, one's complements the contents of the register and adds the data on the right serial-data line to the contents of the register. Any resulting carry can leave on the left serial-data line. The overflow indicator does not change state.

- In Mode 1, two's complements, the contents of the register and permits any carry to leave on the left serial-data line. No data can enter the right serial-data line. The overflow indicator does not change state. The CARRY-IN is set to zero.

- In Mode 2, one's complements the contents of the register and adds the data on the right serial-data line to the contents of the register. Carries cannot leave the left serial data line. The absence or presence of an overflow alters the overflow indicator.

- In Mode 3, two's complements the contents of the register. Serial data can neither enter the right serial-data line nor leave the left serial-data line. The overflow indicator is at zero. The CARRY-IN is set to zero.

- NO-OP no operation takes place. The clock input is inhibited and the state of all registers and indicators remains unchanged.

#### SERIAL-SHIFT OPERATIONS

a. ROTATE (cycle) RIGHT – This operation is internal. The contents of the register shift to the right, cyclic fashion with the leftmost stage accepting data from the rightmost stage regardless of the mode. Data can leave the register serially on the right data line only while the register is in Mode 2 or Mode 0. Data can enter the left data line serially while the register is in Mode 1 or Mode 0. The Ro1 terminal of the "Most Significiant" CD4057A must be connected to the Ro2 terminal of the "Least Significant" CD4057A. All other Ro1 and Ro2 terminals must be left floating. When only one CD4057A is used, Ro1 must be connected to Ro2.

- b. **RIGHT SHIFT** The contents of the register shift to the right and serial operations are as follows:

- In Mode 0, data can enter serially on the left data line, shift through the register, and leave on the right data line.

- In Mode 1, data can enter serially on the left data line. The right data line effectively is opencircuited.

- In Mode 2, data can leave serially on the right data line. The left data line effectively is opencircuited. Vacant spaces are filled with zeros.

- In Mode 3, serial data can neither enter nor leave the register; however, the contents shift to the right and vacated places are filled with zeros.

In all modes, with the DATA OUT control "high" the data is presented on the parallel data lines (D1-D4).

- LEFT SHIFT The contents of the register shift to the left and serial operations are as follows:

- In Mode 0, data can enter the right data line, shift through the register, and leave on the left data line.

- In Mode 1, data can leave serially on the left data line. The right data line effectively is opencircuited. All vacant positions are filled with zeros.

- In Mode 2, data can enter serially on the right data line. The left data line effectively is opencircuited.

- In Mode 3, data can neither enter nor leave the register; however, the contents shift to the left, and vacated places are filled with zeros.

In all modes, with the DATA OUT control "high" the data is presented on the parallel data lines (D1-D4).

Because the "DATA OUT" control instruction is independent of the other 16 instructions, care must be taken not to activate this control when data are to be loaded into the processor. This instruction should only be activated when the processor is executing a NO-OP, any SHIFT, SMZ, COUNT UP or DOWN, CLEAR, or SET.

If a data line, serial or parallel, is used as an input and the logic state of that line is not defined (i.e., the line is an open circuit), then the result of any operation using that line is undefined.

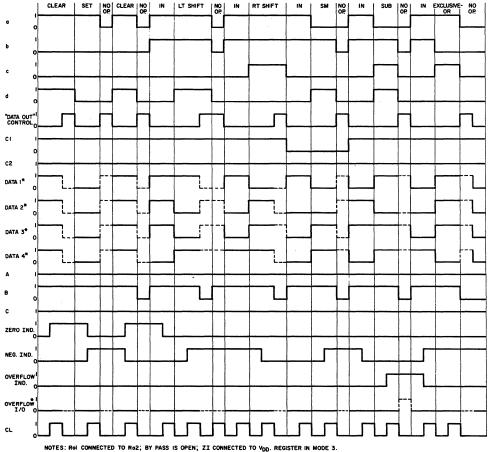

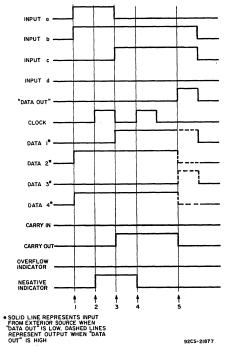

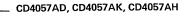

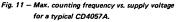

NOTES: Rol CONNECTED TO Ro2; BY PASS IS OPEN; ZI CONNECTED TO VDD. REGISTER IN MODE 3. \*Solid line represents input from externor source when "data out" is low; dashed line represents output when "data out"; ingh.

92CL-2025IRI

# OPERATIONAL SEQUENCE FOR ARITHMETIC ADD CYCLE

- 1. Apply IN Instruction and Word A on Parallel Data Lines (D1-D4).

- 2. Apply CLOCK to load Word A into the register.

- 3. Apply OP CODE Instruction and Word B on Data Lines.

- Apply CLOCK to load resulting function of A and B into the register.

- Apply "DATA OUT" control to present result to Parallel Data Lines.

NOTE: Transitions of Step 2 and Step 3 may occur almost simultaneously; i.e. separated by only one data-hold time.

Fig. 9 - Add cycle waveforms.

#### ZERO DETECTION

The condition of "all zeros" is indicated by a "1" on the Zero Indicator terminal of the "Most Significant" CD4057A. As shown in Fig. 7, terminal ZI of the CD4057A containing the least significant set of bits is connected to  $V_{DD}$ . Zero indication is independent of modes.

#### **NEGATIVE-NUMBER DETECTION**

The NEG IND terminal of the CD4057A is connected to the output of the flip-flop that is in the most significant bit position. A "1" on the NEG IND terminal indicates a negative number is in the register. This detection is also independent of modes.

#### COMPLEMENTING NUMBERS

- 1. One's complement of number in ALU register.

- a) ALU must be in MODE 0 or MODE 2.

- b) Zero on Rt. Data Line.

- c) Execute an SMZ instruction.

- 2. One's complement of number to be loaded into ALU register.

- a) If zero indicator output is low, execute a CLEAR instruction, and make Rt. Data Line = 0.

- b) ALU must be in MODE 0 or MODE 2.

- c) Execute an SUB instruction.

- 3. Two's complement of number in ALU register.

- a) ALU must be in MODE 1 or MODE 3.

b) Execute an SMZ instruction.

- Two's complement of number to be loaded into ALU register.

- a) If zero indicator output is low, execute a CLEAR instruction, and make Rt. Data Line = 0.

- b) ALU must be in MODE 1 or MODE 3.

- c) Execute an SUB instruction.

The following algorithms are given as a general guideline to demonstrate some of the capabilities of the CD4057A.

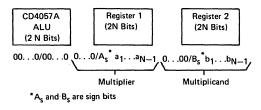

#### MULTIPLICATON OF TWO N-BIT NUMBERS

Multiplication Algorithm

- 1. Clear ALU to Zero

- 2. Store A<sub>s</sub> ⊕ B<sub>s</sub> in External Flip-Flop.

- 3. If  $A_c = 1$ , Complement Register 1.

- 4. If B<sub>s</sub> = 1, Complement Register 2.

- 5. Load Register 2 into ALU.

- Do Shift Left on ALU N Times (N = number of bits).

- 7. Do N Times:

- (1)

- a) If MSB of ALU = 1 (Negative Indicator = High), Then shift ALU left 1 bit; add Register 1 to ALU.

Answer in ALU.

**Division Algorithm**

- 1. Store A<sub>s</sub> ⊕ B<sub>s</sub> in External Flip-Flop.

- 2. If A<sub>s</sub> = 1, complement ALU 1 and ALŪ 2.

- 3. If B<sub>s</sub> = 1, complement Register A.

- 4. Check for Divisor = 0 a) If Divisor = 0; stop, indicates division by 0. b) If Divisor ≠ 0: continue.

- 5. Apply SUB instruction to ALU 1

- and Register A to ALU 1 data lines. a) If  $C_0 = 0$  (Dividend < Divisor),

- Stop, indicates overflow.

- b) If  $C_0 = 1$  (Dividend  $\geq$  Divisor), Continue.

- 6. Put a zero on RT. data line of ALU 2 and shift ALU 1 & ALU 2 left 1 hit

- 7. Do "N" times. Apply SUB instruction to ALU 1 and Register A to ALU 1 data lines. a) If Co = 1, then clock ALU 1, and put a 1 on right data line of ALU 2.

b) If C<sub>0</sub> = 0, then no clock, and put a 0 on right data line of ALU 2.

- 8. If sign Flip Flop = 1, complement ALU 2.

- 9. Answer in ALU 2.

#### CONDITIONAL OPERATION

Inhibition of the clock pulse can be accomplished with a programmed NO-OP instruction or through conditional input terminals A. B. and C. In a system of many CD4057A's, each CD4057A can be made to automatically control its own operation or the operation of any other CD4057A in the system in conjunction with the Overflow, Zero, or Negative (Number) indicators. Table II, the conditional-inputs truth table, defines the interactions among A, B, and C.

#### TABLE II - CONDITIONAL-INPUTS TRUTH TABLE

| A | в | с | OPERATION<br>PERMITTED |

|---|---|---|------------------------|

| 0 | х | х | Yes                    |

| 1 | 0 | 0 | Yes                    |

| 1 | 0 | 1 | No                     |

| 1 | 1 | 0 | No                     |

| 1 | 1 | 1 | Yes                    |

X = don't care

Two examples of how the conditional operation can be used are as follows:

- 1) For the Multiplication Algorithm

- A = 1, for step 7 (1) A = 0, for step 7 (2)

- B = 1

- C = negative Indicator

- 2) For the Division Algorithm

- A = 1, for step 7 (1)

- A = 0, for step 7 (2)

- B = 1

- C = Co (left data line)

#### **OVERFLOW DETECTION**

The CD4057A is capable of detecting and indicating the presence or absence of an arithmetic two's-complement overflow. A two's-complement overflow is defined as having occurred if the signs of the two initial words are the same and the sign of the result is different while performing a carry-generating instruction.

Overflows can be detected and indicated only during operation in Mode 2 or Mode 3 and can occur for only four instructions (AD, SMZ, SM, and SUB). If an overflow is detected and stored in the overflow flip-flop, any one of the five instructions AD, SMZ, SM, SUB, or IN can change the overflow indicator.

When any of the three subtraction instructions is used, the sign bit of the data being subtracted is complemented and this value is used as one of the two initial signs to detect overflows. If an overflow has occurred, the final sign of the sum or difference is one's complemented and stored in the most-significant-bit position of the register.

The overflow flip-flop is updated at the same time the new result is stored in the CD4057A. Whenever data on the parallel-data lines are loaded into the CD4057A, whatever is on the Overflow I/O line is loaded into the overflow flip-flop. Also, whenever data are dumped on the parallel data lines from the CD4057A, the contents of the overflow flip-flop are dumped on the Overflow 1/0 line. Thus overflows may be stored elsewhere and then fed into the CD4057A at another time.

### OPERATIONAL SEQUENCE AND WAVEFORMS FOR PROPAGATION-DELAY MEASUREMENTS

- 1. DATA IN-to-CARRY OUT and DATA IN-to-SUM OUT

- A. Apply Word A and IN instruction

- B. Apply Clock to load word A into register

- C. Apply AD instruction

- D. Apply Word B (data in)

- E. Apply Clock to load result (sum out)

- F. Apply DATA OUT CONTROL to look at result

G

#### 2. CARRY IN-to-CARRY OUT and CARRY IN-to-SUM OUT

- A. Apply Word A and IN instruction

- B. Apply Clock to load word A into register

- C. Apply AD instruction

- D. Apply Word B

- E. Apply CARRY IN (carry in)

- F. Apply Clock to load result (sum out)

- G. Apply DATA OUT CONTROL to look at result

C D

Fig. 10(a) - DATA IN-to-CARRY OUT and DATA IN-to-SUM OUT.

Fig. 10(b) - CARRY IN-to-CARRY OUT and CARRY IN-to-SUM OUT.

Fig.12 - Transition time vs. load capacitance for Data Outputs (D1-D4).

9205-21879

Fig. 14 - Data setup time.

File No. 635

Fig. 15 – Data hold time.

**TEST CIRCUITS**

Fig.16 – Noise immunity for "SET" instruction (see Timing Diagram)

#### TYPICAL APPLICATION

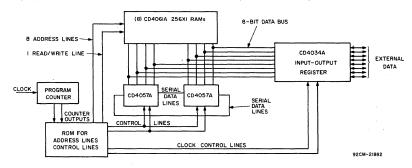

The CD4057A has been designed for use as a parallel processor in flexible, programmable, easily expandable, special or general purpose computers, where minimization of exter-

Fig. 17 - Quiescent device current.

nal connections and data busing are primary design goals. The block diagram of Fig. 18 is an example of a computer that processes 8 bits in parallel.

Fig. 18 – Example of Computer Organization Using CD4057A.